g2057+基于FPGA的目标跟踪算法实现verilog(300元)

- 模板:¥300.00

- 成品编号:jgy2057

- 使用技术:FPGA

- 数据库:无

- 最后更新:2018-09-01 18:42

注意:QQ1764030875,qq1834660615为本网站唯一成品的账号,其他均为盗版

计算机毕业设计源码网:我们提供的源码通过邮箱或者QQ传送,如果有啥问题直接联系客服

素材描述:

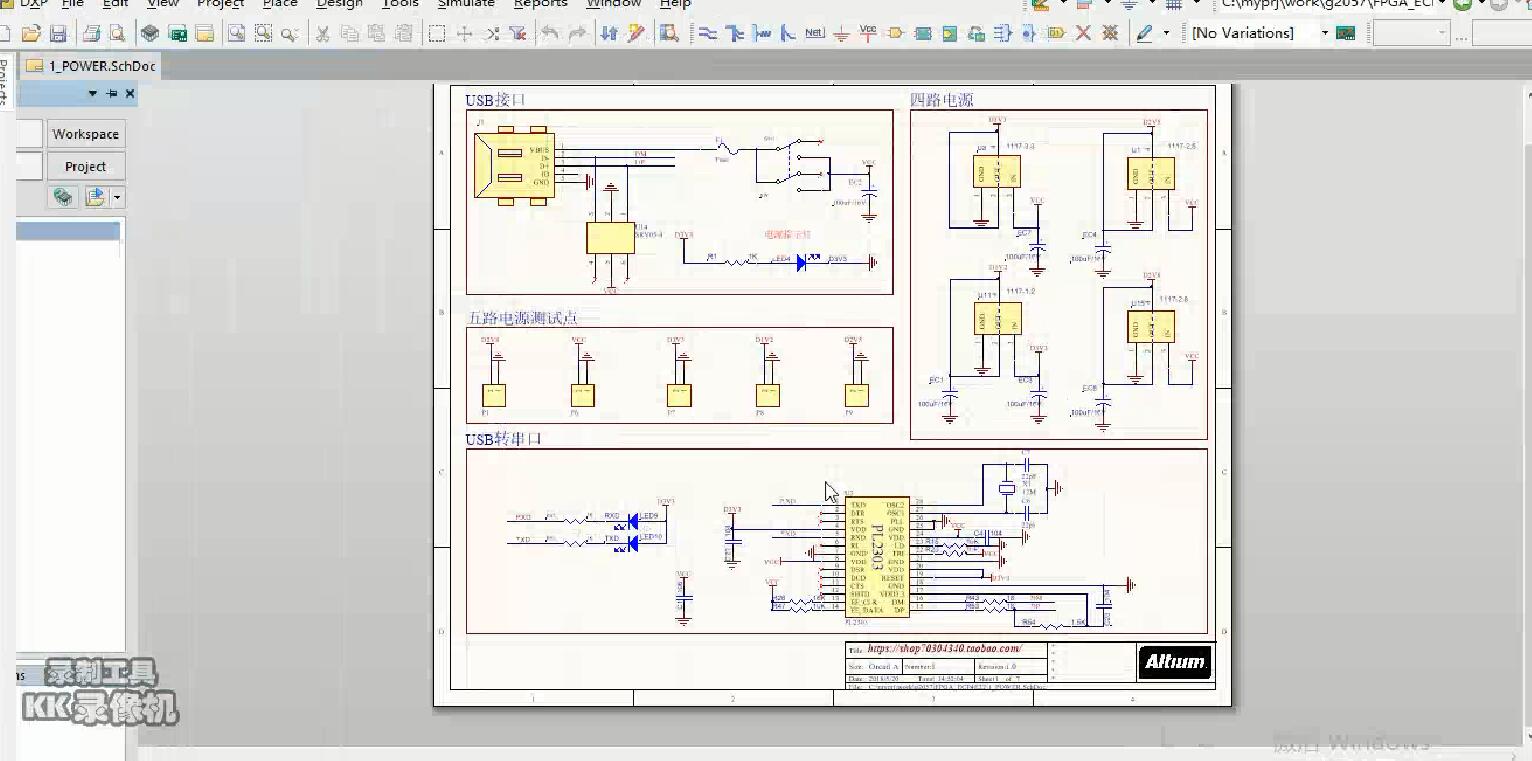

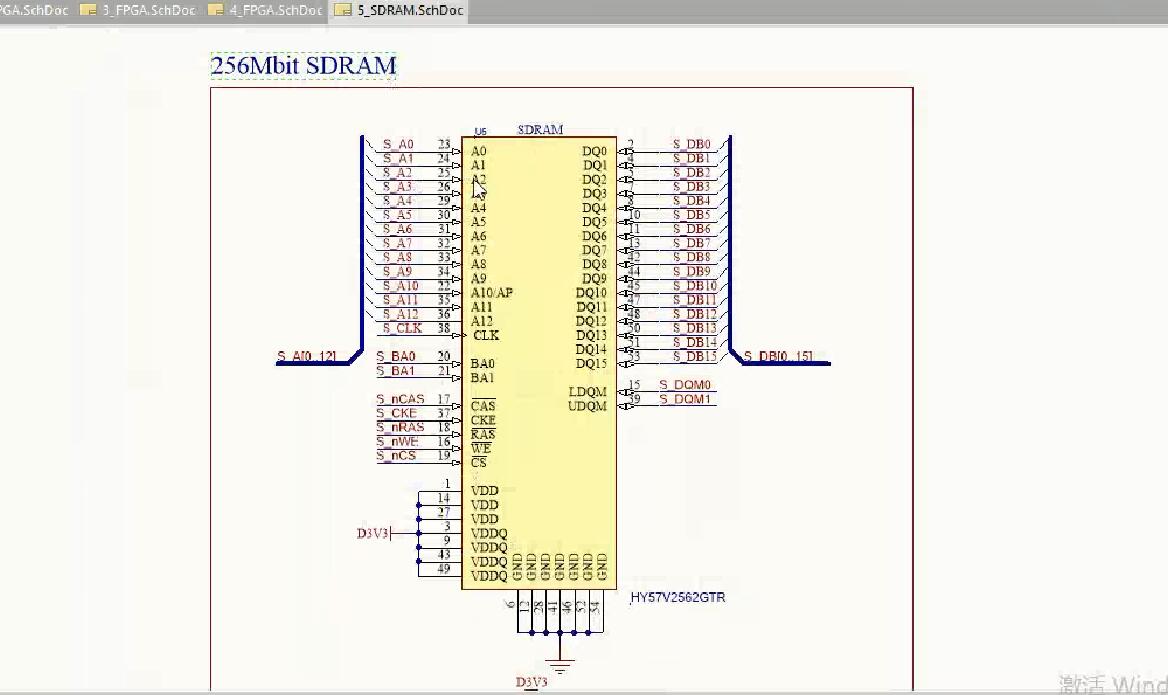

本套fpga设计包含程序,原理图,演示视频

完成基于FPGA的目标跟踪算法的逻辑实现。

具体内容:

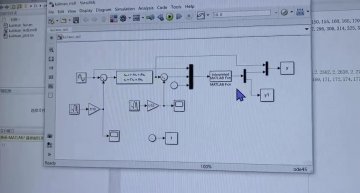

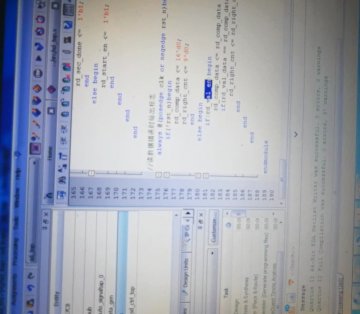

使用Verilog作为硬件描述语言,然后在ISE14.7的开发平台上完成电路设计,功能仿真,综合,实现这一系列步骤对所设计的逻辑功能进行实验调试。在实现过程结束后需要做时序仿真,之后用ISE自带的工具,加载到FPGA中,进行在线调试,评估是否较好的实现了目标跟踪算法,并进行修改调试,最终达到较为满意的效果。

设计思路:

采取使用基于背景差分检测的 SAD 匹配跟踪算法对目标进行跟踪。即跟踪之前,先采用背景差分法检测出运动目标,并采用形心定位的方法,确定运动目标所在的位置,并提取出运动目标模板,然后用提取出的模板图像进行匹配跟踪。

展示效果:

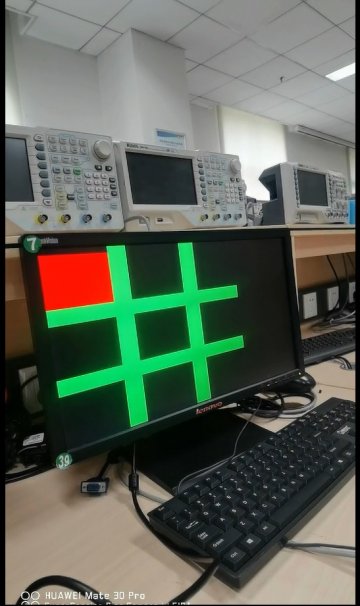

通过串口向开发板输入序列图像,只有在第一张图像中标注需要跟踪的对象,之后每一张的图像中都能对第一张图像中的对象进行跟踪,即框出所选择的对象,这些图像都能通过vga端口显示在显示器上。

具体内容:

使用Verilog作为硬件描述语言,然后在ISE14.7的开发平台上完成电路设计,功能仿真,综合,实现这一系列步骤对所设计的逻辑功能进行实验调试。在实现过程结束后需要做时序仿真,之后用ISE自带的工具,加载到FPGA中,进行在线调试,评估是否较好的实现了目标跟踪算法,并进行修改调试,最终达到较为满意的效果。

设计思路:

采取使用基于背景差分检测的 SAD 匹配跟踪算法对目标进行跟踪。即跟踪之前,先采用背景差分法检测出运动目标,并采用形心定位的方法,确定运动目标所在的位置,并提取出运动目标模板,然后用提取出的模板图像进行匹配跟踪。

展示效果:

通过串口向开发板输入序列图像,只有在第一张图像中标注需要跟踪的对象,之后每一张的图像中都能对第一张图像中的对象进行跟踪,即框出所选择的对象,这些图像都能通过vga端口显示在显示器上。

标签

全部评论 / 0