2004+FPGA做一个电子钟verilog(500元)

- 模板:¥500.00

- 成品编号:wlq2004

- 使用技术:FPGA

- 数据库:无

- 最后更新:2018-11-23 18:12

注意:QQ1764030875,qq1834660615为本网站唯一成品的账号,其他均为盗版

计算机毕业设计源码网:我们提供的源码通过邮箱或者QQ传送,如果有啥问题直接联系客服

素材描述:

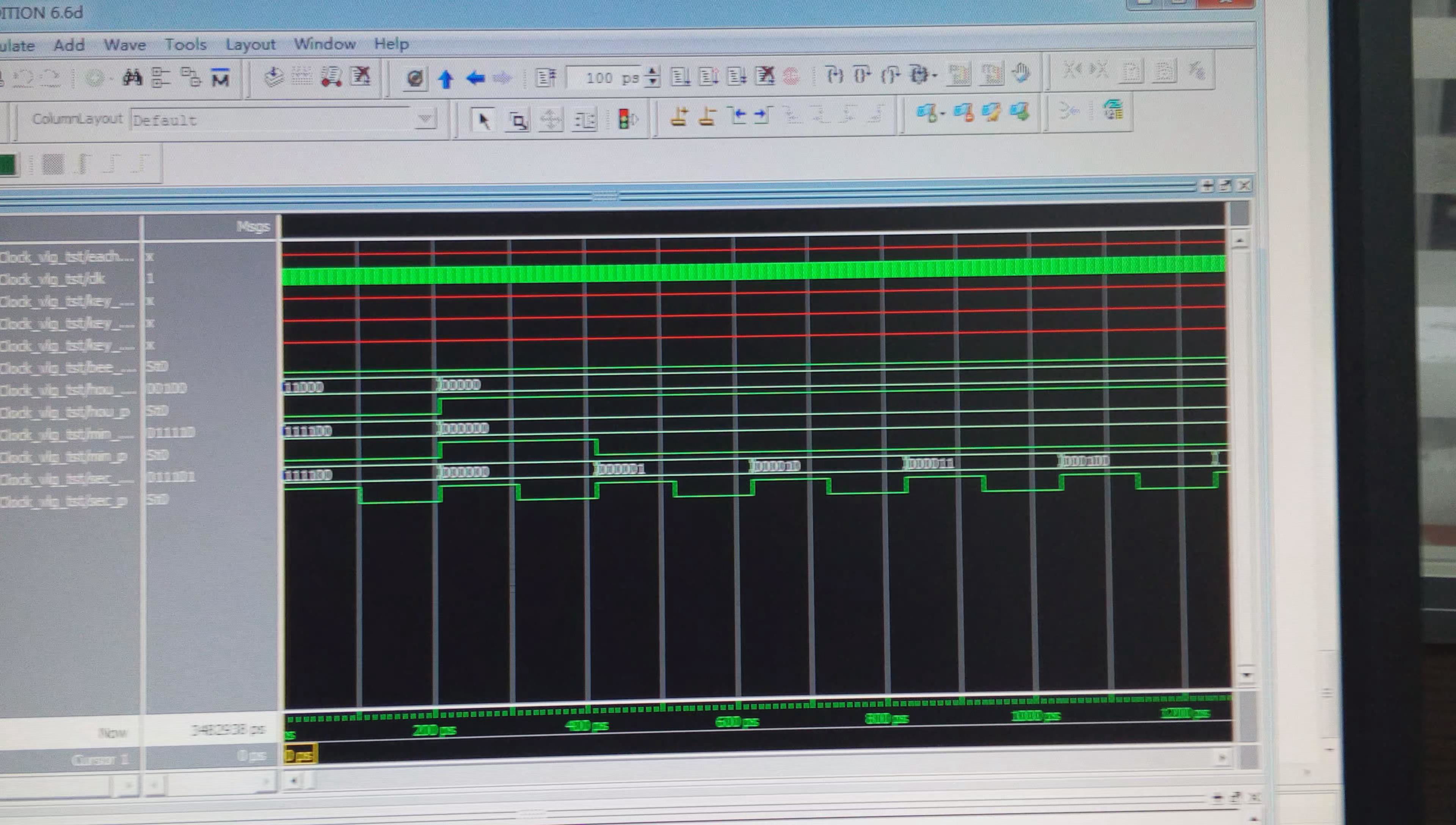

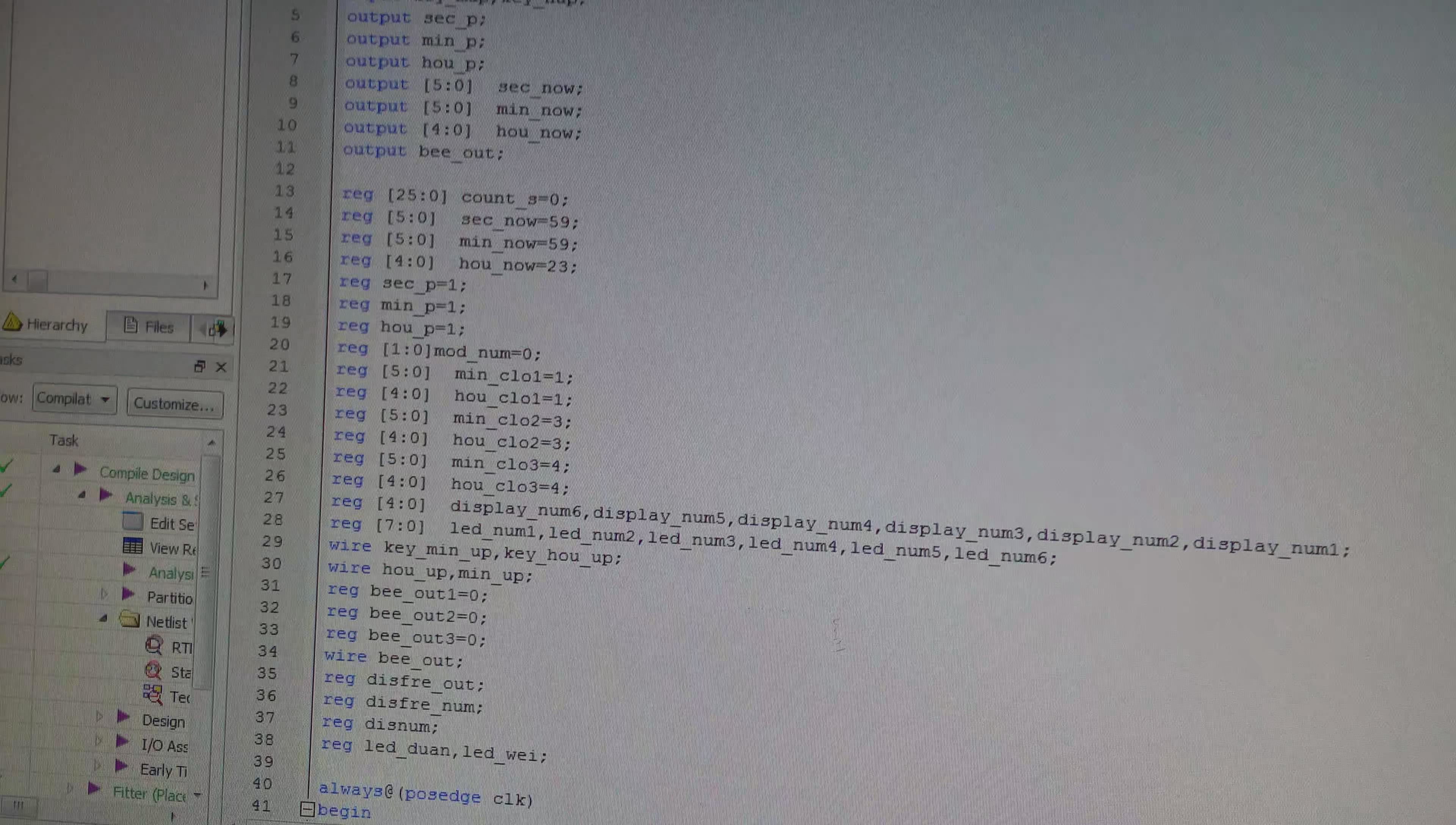

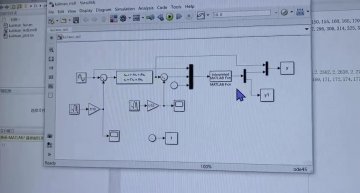

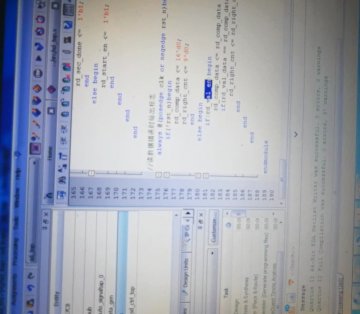

本套fpga设计包含程序仿真,1w字论文

数字电子钟系统设计功能要求如下:

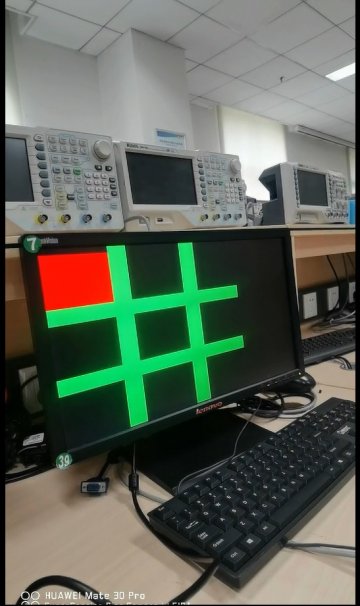

1、采用数码管显示时、分、秒

2、精度为1s

3、可对时间进行预置和修改

4、可设置3组闹钟

5、闹铃时间发出声光提示信息

系统设计方案

根据数字电子钟的功能要求,有三种设计方案可供选择,方案一为采用低集成度逻辑芯片实现,方案二采用微控制器实现,方案三采用FPGA实现。下面分别介绍各种实现方案的优势及缺点。

方案一:采用低集成度的逻辑芯片。第一个晶体管是作为分立元件提供的,后来随着微电子技术的提升,开始将整个电路制作在一块半导体上,此方法最初是由英国雷达专家G.W.A.Dummer在1952年提出的,到1958年德州仪器公司成功将包含5个元件的移相震荡器集成到一片半导体芯片上。几乎是同一时期,两位飞思卡尔的公司的创建者发明了衬底光学印刷技术,此技术已经广泛应用在制造芯片中的晶体管、绝缘层和连接线。上世纪六十年代中期,德州仪器公司设计生产了大量基础设计芯片,成为54系列和74系列。这些小芯片包含少量简单逻辑门,可实现与、非、计数以及加减等功能。

此类芯片优势在于价格低廉。但是由于此类芯片集成度较低,功能简单,只能实现基础任务,因此需要大量芯片级联配合,这就造成了电路板面积大,走线复杂,电路板一旦成型,后期修改维护升级困难。

方案二:采用单片机等微控制器。上世纪六七十年代是数字IC技术飞速发展的时期。1971年Intel公司开发出世界上第一个微处理器4004,包含2300个晶体管,每秒可执行60000次操作。经过几十年的发展,虽然微控制器的性能在不断提升,但是微控制器的结构却没有发生变化,仍然是主控制器核心,在外围集成通用输入输出、定时计数中断等外设实现的。

编写的每一条微控制器程序都需要执行数目不等的多条机器指令,这也就导致了微控制器不能进行高速实时运算,只适合做一些逻辑控制任务。虽然也有定时器等时间控制外设,但是其处理存在延时,不能很好的实现高速实时控制。

方案三:采用FPGA进行设计。FPGA是建立在可编程思想上设计的门电路。每个FPGA拥有大量的可编程逻辑块,通过适当的编程单元可以配置这些可编程逻辑块,使得每个可编程逻辑块可以执行不同的功能。

完整的FPGA包括大量的可编程逻辑块,周围是可编程的高速信号线。在FPGA中可以轻易的产生通用输入输出接口,通信接口等外设,因此可在不改变外围硬件连接的前提下通过更改FPGA软件程序实现设计功能的修改和扩展。

通过综合比对三种可行方案,最终选择方案三采用FPGA进行设计。

标签

全部评论 / 0